- 品牌

- 上海伟诺

- 型号

- 伟诺

- 适用行业

- 半导体

- 版本类型

- 网络版

- 语言版本

- 简体中文版

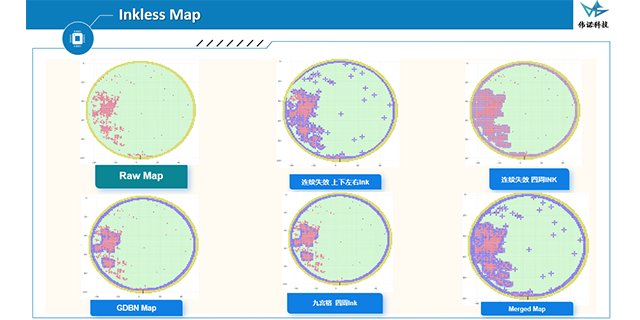

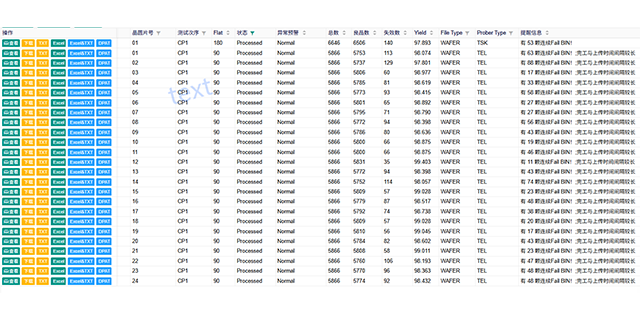

面对国产半导体制造对自主可控软件的迫切需求,良率管理系统成为打通数据孤岛、实现质量闭环的关键工具。系统自动采集ETS88、93k、J750、Chroma等主流Tester平台输出的stdf、csv、xls、log、spd、jdf、zip、txt等多种格式测试数据,通过内置算法识别重复项、缺失值并过滤异常记录,确保后续分析基于高可信度数据源。在标准化数据库支撑下,企业可从时间维度追踪良率趋势,或聚焦晶圆特定区域对比缺陷分布,快速定位工艺波动点。结合WAT、CP与FT参数的联动分析,进一步揭示影响良率的深层原因。SYL与SBL的自动计算与卡控机制,强化了过程质量防线。灵活的报表工具支持按模板生成日报、周报、月报,并导出为PPT、Excel或PDF格式,提升跨部门协同效率。上海伟诺信息科技有限公司自2019年成立以来,专注打造适配本土需求的YMS系统,助力构建中国半导体软件生态。Mapping Over Ink处理提升产品市场竞争力,降低客户投诉率。辽宁可视化MappingOverInk处理平台

每日晨会前临时整理良率报表,常因数据口径不一引发争议。YMS系统按预设模板自动生成日报、周报、月报,内容涵盖良率趋势、区域缺陷分布、WAT/CP/FT关联分析等关键指标,并支持一键导出为PPT、Excel或PDF格式。生产主管可用PPT版直接汇报,质量工程师调取Excel原始数据深入挖掘,客户审计则接收标准化PDF文档。自动化流程消除手工汇总误差,确保全公司使用同一套可靠数据。报告生成时间从数小时压缩至分钟级,大幅提升跨部门协同效率。上海伟诺信息科技有限公司通过灵活报表工具,让数据真正服务于决策闭环。广西晶圆GDBC软件UPLY处理针对特定层间关联缺陷,通过垂直面算法判定单颗Die失效概率。

在半导体制造中,晶圆厂制程的任何微小变动,都可能引起良率与可靠性的风险。其中,一个尤为典型的系统性失效模式,便源于光刻环节的Reticle(光罩)。当Reticle本身存在污染、划伤或设计瑕疵时,或当光刻机在步进重复曝光过程中出现参数漂移(如焦距不准、曝光能量不均)时。这些因Reticle问题而产生的特定区域内的芯片,实质上构成了一个高风险的“潜伏失效群体”。若不能在测试阶段被精确识别并剔除,将直接流向客户端,对产品的长期可靠性与品牌声誉构成严重威胁。识别并处理这类与Reticle强相关的潜在缺陷,是现代高可靠性质量管理中一项极具挑战性的关键任务。

上海伟诺信息科技有限公司在Mapping Over Ink功能中提供了一个Shot Mapping Ink方案,可以将整个Mapping按Reticle大小或是自定义大小的方格,根据设定的算法将整个Shot进行Ink, 从而去除掉因光刻环节的Reticle引起的潜在性失效芯片。通过Shot Mapping Ink方案,用户能够将质量管控的关口从“筛查单个失效芯片”前移至“拦截整个失效风险区域”。这尤其适用于对可靠性要求极严苛的车规、工规等产品,它能极大程度地降低因光刻制程偶发问题导致的批次性可靠性风险,为客户构建起一道应对系统性缺陷的坚固防线。

面对海量测试数据,表格形式难以快速捕捉异常模式。YMS系统将良率与缺陷信息转化为热力图、趋势曲线、散点图等多种可视化图表:晶圆热力图一眼识别高缺陷区域,时间序列图揭示良率波动周期,参数散点图暴露非线性关联关系。例如,通过CP漏电与FT功能失效的散点分布,可判断是否存在特定电压下的共性失效机制。图形化表达降低数据分析门槛,使非数据专业人员也能参与质量讨论。这种“所见即所得”的洞察方式,加速了从数据到行动的转化。上海伟诺信息科技有限公司以可视化为关键设计原则,提升YMS的信息传达效率与决策支持价值。DPAT模块动态调整阈值以适应批次差异,分场景优化测试限设定。

晶圆级良率监控要求系统能处理高密度、高维度的测试数据流。YMS方案自动对接ASL1000、TR6850、MS7000、SineTest等设备,实时汇聚原始测试结果并完成结构化清洗,消除人工干预带来的延迟与误差。系统以图表形式直观呈现晶圆热力图,清晰展示边缘、中心或象限区域的良率差异,辅助工程师判断光刻、刻蚀或沉积环节的均匀性问题。当某批次CP良率异常时,可联动WAT参数变化追溯前道工艺漂移,实现从前端到后端的全链路追溯。多周期报表自动生成并支持多格式导出,满足从产线到高管的信息消费习惯。这种深度可视化与智能关联分析能力,使良率管理从经验驱动转向数据驱动。上海伟诺信息科技有限公司凭借对半导体制造流程的理解,将YMS打造为晶圆厂提质增效的有效工具。工艺工程师基于GDBC聚类结果优化制程参数,提升制造良率水平。广西晶圆GDBC软件

失效Die的空间分布特征是判断工艺问题的关键依据,指导制程参数优化。辽宁可视化MappingOverInk处理平台

在半导体制造中,由于Fab制程的物理与化学特性,晶圆边缘的芯片(Edge Die)其失效率明显高于中心区域。这一现象主要源于几个关键因素:首先,在光刻、刻蚀、薄膜沉积等工艺中,晶圆边缘的反应气体流场、温度场及压力场分布不均,导致工艺一致性变差;其次,边缘区域更容易出现厚度不均、残留应力集中等问题;此外,光刻胶在边缘的涂覆均匀性也通常较差。这些因素共同导致边缘芯片的电气参数漂移、性能不稳定乃至早期失效风险急剧升高。因此,在晶圆测试(CP)的制造流程中,对电性测试图谱(Wafer Mapping)执行“去边”操作,便成为一项提升产品整体良率与可靠性的关键步骤。

上海伟诺信息科技有限公司Mapping Over Ink功能中的Margin Map功能提供多种算法与自定义圈数,满足客户快速高效低剔除边缘芯片,可以从根本上避免后续对这些潜在不良品进行不必要的封装和测试,从而直接节约成本,并确保出厂产品的质量与可靠性要求。辽宁可视化MappingOverInk处理平台

上海伟诺信息科技有限公司是一家有着雄厚实力背景、信誉可靠、励精图治、展望未来、有梦想有目标,有组织有体系的公司,坚持于带领员工在未来的道路上大放光明,携手共画蓝图,在上海市等地区的数码、电脑行业中积累了大批忠诚的客户粉丝源,也收获了良好的用户口碑,为公司的发展奠定的良好的行业基础,也希望未来公司能成为*****,努力为行业领域的发展奉献出自己的一份力量,我们相信精益求精的工作态度和不断的完善创新理念以及自强不息,斗志昂扬的的企业精神将**和您一起携手步入辉煌,共创佳绩,一直以来,公司贯彻执行科学管理、创新发展、诚实守信的方针,员工精诚努力,协同奋取,以品质、服务来赢得市场,我们一直在路上!

- 内蒙古半导体PAT工具 2026-04-06

- 湖南GDBC系统 2026-04-06

- 福建晶圆MappingOverInk处理服务商 2026-04-06

- 上海晶圆GDBC平台 2026-04-06

- 广西Mapping Inkless软件 2026-04-06

- 四川GDBC系统定制 2026-04-06

- 天津可视化PAT平台 2026-04-06

- 江西可视化Mapping Inkless系统定制 2026-04-06