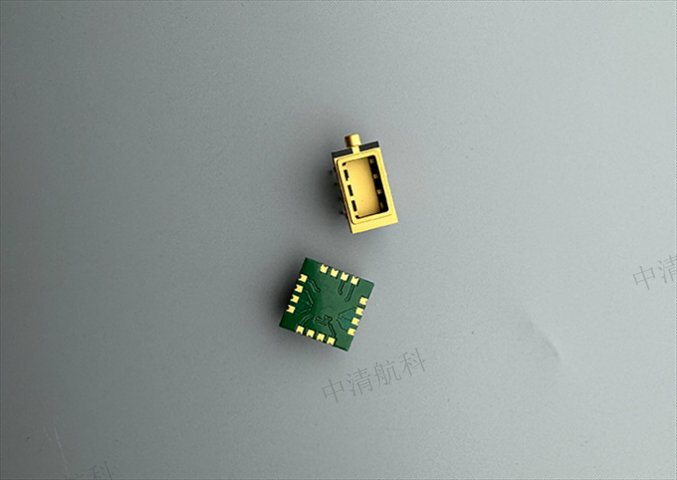

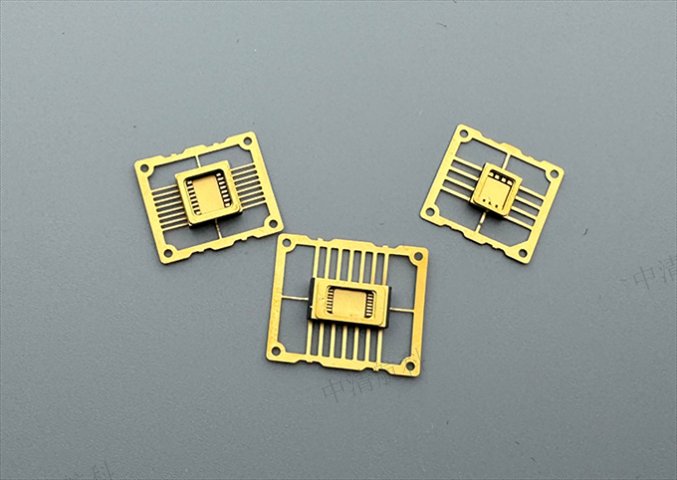

面对量子比特超导封装难题,中清航科开发蓝宝石基板微波谐振腔技术。通过超导铝薄膜微加工,实现5GHz谐振频率下Q值>100万,比特相干时间提升至200μs。该方案已用于12量子比特模块封装,退相干率降低40%,为量子计算机提供稳定基础。针对AI边缘计算需求,中清航科推出近存计算3D封装。将RRAM存算芯片与逻辑单元垂直集成,互连延迟降至0.1ps/mm。实测显示ResNet18推理能效达35TOPS/W,较传统方案提升8倍,满足端侧设备10mW功耗要求。微型芯片封装难度大,中清航科微缩技术,实现小体积承载强性能。浙江半导体封装贴片

芯片封装的发展历程:自20世纪80年代起,芯片封装技术历经多代变革。从早期的引脚插入式封装,如DIP(双列直插式封装),发展到表面贴片封装,像QFP(塑料方形扁平封装)、PGA(针栅阵列封装)等。而后,BGA(球栅阵列封装)、MCP(多芯片模块)、SIP(系统级封装)等先进封装形式不断涌现。中清航科紧跟芯片封装技术发展潮流,不断升级自身技术工艺,在各个发展阶段都积累了丰富经验,能为客户提供符合不同时期技术标准和市场需求的封装服务。上海ic的气密性封装超算芯片多芯片协同,中清航科先进封装,降低芯片间数据传输延迟。

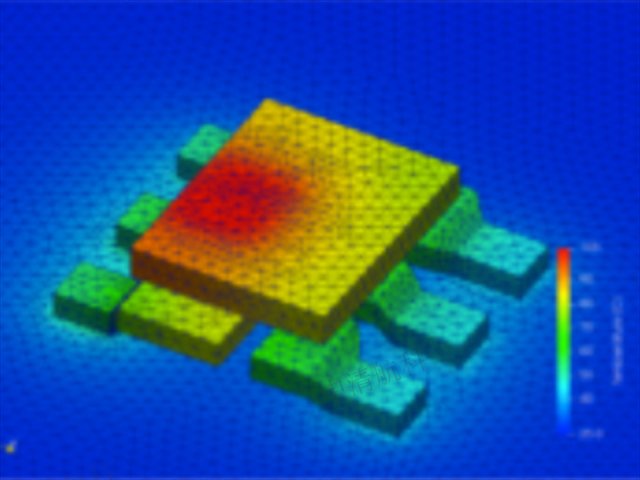

中清航科在芯片封装领域的优势-技术实力:中清航科拥有一支由专业技术人才组成的团队,他们在芯片封装技术研发方面经验丰富,对各类先进封装技术有着深入理解和掌握。公司配备了先进的研发设备和实验室,持续投入大量资源进行技术创新,确保在芯片封装技术上始终保持带头地位,能够为客户提供前沿、质优的封装技术解决方案。中清航科在芯片封装领域的优势-设备与工艺:中清航科引进了国际先进的芯片封装设备,构建了完善且高效的生产工艺体系。从芯片的预处理到封装完成,每一个环节都严格遵循国际标准和规范进行操作。通过先进的设备和优化的工艺,公司能够实现高精度、高可靠性的芯片封装,有效提高产品质量和生产效率,满足客户大规模、高质量的订单需求。

中清航科WLCSP测试一体化方案缩短生产周期。集成探针卡与临时键合层,实现300mm晶圆单次测试成本降低40%。在PMIC量产中,测试覆盖率达99.2%。面向航天应用,中清航科抗辐照封装通过MIL-STD-750认证。掺铪二氧化硅钝化层使总剂量耐受>300krad,单粒子翻转率<1E-10error/bit-day。已服务低轨卫星星座项目。中清航科MEMS真空封装良率突破98%。采用多孔硅密封技术,腔体真空度维持<0.1Pa十年以上。陀螺仪零偏稳定性达0.5°/h,满足导航级应用。中清航科深耕芯片封装,从设计到量产全流程优化,缩短产品上市周期。

针对MicroLED巨量转移,中航清科开发激光释放转印技术。通过动态能量控制实现99.99%转移良率,支持每小时500万颗芯片贴装。AR眼镜像素密度突破5000PPI。基于忆阻器交叉阵列,中清航科实现类脑芯片3D封装。128×128阵列集成于1mm²面积,突触操作功耗<10pJ。脉冲神经网络识别准确率超96%。中清航科超导芯片低温封装解决热应力难题。采用因瓦合金基板,在4K温区热失配<5ppm/K。量子比特频率漂移控制在±0.1GHz,提升多比特纠缠保真度。芯片封装可靠性需长期验证,中清航科加速老化测试,提前暴露潜在问题。玻璃封装外壳

芯片封装测试环节关键,中清航科全项检测,确保出厂芯片零缺陷。浙江半导体封装贴片

面对卫星载荷严苛的空间环境,中清航科开发陶瓷多层共烧(LTCC)MCM封装技术。采用钨铜热沉基底与金锡共晶焊接,实现-196℃~+150℃极端温变下热失配率<3ppm/℃。通过嵌入式微带线设计将信号串扰抑制在-60dB以下,使星载处理器在单粒子翻转(SEU)事件率降低至1E-11errors/bit-day。该方案已通过ECSS-Q-ST-60-13C宇航标准认证,成功应用于低轨卫星星务计算机,模块失效率<50FIT(10亿小时运行故障率)。针对万米级深海探测装备的100MPa超高压环境,中清航科金属-陶瓷复合封装结构。采用氧化锆增韧氧化铝(ZTA)陶瓷环与钛合金壳体真空钎焊,实现漏率<1×10⁻¹⁰Pa·m³/s的密封。内部压力补偿系统使腔体形变<0.05%,保障MEMS传感器在110MPa压力下精度保持±0.1%FS。耐腐蚀镀层通过3000小时盐雾试验,已用于全海深声呐阵列封装,在马里亚纳海沟实现连续500小时无故障探测。浙江半导体封装贴片